### International Journal of Engineering& Scientific Research

Vol.13 Issue 07, July 2025

ISSN: 2347-6532 Impact Factor: 8.076

Journal Homepage: <a href="http://www.ijmra.us">http://www.ijmra.us</a>, Email: editorijmie@gmail.com

Double-Blind Peer Reviewed Refereed Open Access International Journal - Included in the International Serial Directories Indexed & Listed at: Ulrich's Periodicals Directory ©, U.S.A., Open J-Gage as well as in Cabell's Directories of Publishing Opportunities, U.S.A

### Real-Time Ultrasonic Sensing: FPGA-Based Implementation and Optimization

# Saurav Somany Institute of Technology & Management, Rewari University: Maharshi Dayanand University – Rohtak

#### **Abstract**

This research explores recent advancements in high-precision ultrasonic distance measurement technology, with a particular focus on continuous signal processing capabilities. The primary objective is the architectural design and hardware implementation of an FPGA-based ultrasonic system. This system aims to overcome key limitations associated with traditional ultrasonic ranging methods, such as usability challenges, testing complexities, real-time data processing, and measurement accuracy. Designed to meet the demands of applications like vehicle obstacle avoidance and autonomous navigation, the proposed system seeks to enhance safety and operational efficiency. Ultrasonic ranging is agriculture. extensively used across various sectors—including manufacturing, transportation, environmental monitoring, healthcare, energy management, and scientific research—benefiting from ongoing technological innovations. Critical performance metrics such as measurement precision, distance accuracy, and system robustness are vital for improving the reliability of automated control systems, thereby boosting productivity and fostering scientific and technological progress. Currently, conventional ultrasonic obstacle detection in vehicles typically employ 8-bit or 16-bit microcontrollers to process echo signals and generate collision avoidance signals. This research proposes leveraging FPGA technology to address these limitations through comprehensive simulation and evaluation of the ultrasonic controller. The system's anticipated performance improvements aim to set new benchmarks in safety, accuracy, and real-time responsiveness, advancing ultrasonic ranging capabilities for critical applications.

### INTRODUCTION

Ultrasonic ranging has found widespread applications across various domains, including manufacturing, agriculture, transportation, environmental monitoring, healthcare, defense, and energy management. With advancements in technology, the performance metrics of ultrasonic systems—including the accurate/précised math's calculation, the coverage distance tracked measurmental data, and the long durability assessment—play a significant/crucial role in increasing/enhancing the quality assurance, optimizing production efficiency, and promoting scientific and technical innovations.

### **Problem Statement:**

Traditional ultrasonic distance measurement systems, primarily utilizing 8-bit or 16-bit microcontrollers, face significant limitations in measurement accuracy, real-time processing capabilities, usability, and robustness, which hinder their effectiveness in critical applications such as vehicular obstacle avoidance and autonomous navigation. These limitations impact the system's ability to deliver precise, reliable, and high-speed distance measurements necessary for safety-critical operations. Therefore, there is a pressing need to develop an advanced ultrasonic ranging system that leverages FPGA technology to enhance processing speed, measurement fidelity, and system durability. This research aims to design and implement an FPGA-based ultrasonic device that overcomes the constraints of conventional microcontroller-based systems, providing continuous processing capabilities, improved accuracy, and real-time data handling, thereby advancing the safety, efficiency, and reliability of ultrasonic obstacle detection in various application domains.

### Implementation of the Ultrasonic based Ranged System

The proposed/disclosed FPGA for the critically ultrasonic system architecture will consist of the following subsystems: Ultrasonic Transmitter and Receiver: This module will generate ultrasonic waves and capture the echo return from objects. The timing of the emitted wave and detected echo will be critical for distance measurement accuracy. FPGA Control Module: The FPGA will be responsible for controlling the timing of the ultrasonic transmission and reception, processing the received signals to calculate distance, and interfacing with other system components. User Interface and Output Module: This module will provide real-time feedback to the user, conveying distance readings and system status.

#### **Ultrasonic Sensor Work**

Ultrasonic sensors operate in a way that makes their sound waves too subtle for individuals to detect directly. Instead, these sensors rely on measuring the time difference between emitted and reflected echoes, similar to how radar systems detect targets by analyzing radio wave reflections. Some ultrasonic devices combine transmission and reception functions into a single unit, providing dedicated ultrasound signaling for both sending and receiving signals. This integrated design is suitable for compact, luxury applications, offering a smaller form factor compared to systems with separate components.

Although radar and ultrasonic sensors can serve similar purposes, ultrasonic sensors are widely accessible and often more affordable—sometimes costing just a few pennies—while still providing higher accuracy in certain scenarios. For example, handling transparent plastics is challenging for radar and light-based sensors, but ultrasonic sensors are unaffected by such materials, making them more versatile in various environments.

#### RESULT AND DISCUSSION

These modules will be designed using the Very High DL database and synthesized with the aid of Xilinx's integrated FPGA development environment. The design can be simulated using Xilinx's Xilinx ISE Simulator (Xsimcx). The development is targeted for implementation on the Xilinx XA3-3650-4VQG15 device.

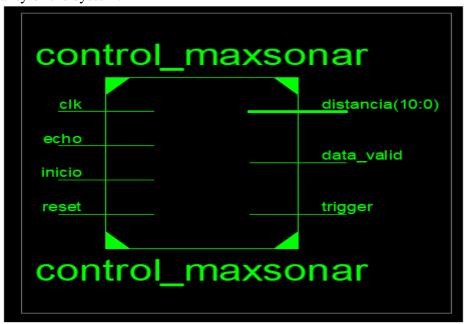

The design serves as an external architectural controller for the ultrasonic sensor system. It primarily includes four input pins and three output pins. The input pins handle clock signals, echo initiation, and reset functions, while the output pins manage trigger signals and other data outputs. The internal RTL schematics illustrate the control logic of the ultrasonic sensor, clearly showing all the integrated devices and their interconnections, ensuring proper functionality of the system.

| control_maxsonar Project Status (05/22/2020 - 22:51:09) |                           |                       |                    |  |  |  |

|---------------------------------------------------------|---------------------------|-----------------------|--------------------|--|--|--|

| Project File:                                           | ultrasonic.xise           | Parser Errors:        | No Errors          |  |  |  |

| Module Name:                                            | control_maxsonar          | Implementation State: | Synthesized        |  |  |  |

| Target Device:                                          | xa3s50-4vqg100            | • Errors:             | No Errors          |  |  |  |

| Product Version:                                        | ISE 13.3                  | Warnings:             | 3 Warnings (0 new) |  |  |  |

| Design Goal:                                            | Balanced                  | Routing Results:      |                    |  |  |  |

| Design Strategy:                                        | Xilinx Default (unlocked) | Timing Constraints:   |                    |  |  |  |

| Environment:                                            | System Settings           | Final Timing Score:   |                    |  |  |  |

| Device Utilization Summary (estimated values) [-] |      |           |             |  |  |  |

|---------------------------------------------------|------|-----------|-------------|--|--|--|

| Logic Utilization                                 | Used | Available | Utilization |  |  |  |

| Number of Slices                                  | 34   | 768       | 4%          |  |  |  |

| Number of Slice Flip Flops                        | 35   | 1536      | 2%          |  |  |  |

| Number of 4 input LUTs                            | 63   | 1536      | 4%          |  |  |  |

| Number of bonded IOBs                             | 17   | 63        | 26%         |  |  |  |

| Number of GCLKs                                   | 2    | 8         | 25%         |  |  |  |

| Detailed Reports [-] |           |                           |        |                    |       |  |

|----------------------|-----------|---------------------------|--------|--------------------|-------|--|

| Report Name          | Status    | Generated                 | Errors | Warnings           | Infos |  |

| Synthesis Report     | Current   | Fri 22. May 22:51:07 2020 | 0      | 3 Warnings (0 new) | 0     |  |

| Toursday Service     | 0.4-60-4- | C 2C A 1E-27-27 2020      | 10     |                    | 10    |  |

#### CONCLUSION THAT WILL UTILIZEFUL FOR FUTURE WORK

This study focuses on the development of a high-precision, real-time ultrasonic spectrum system utilizing FPGA (Field Programmable Gate Array) technology for both architectural design and hardware implementation. The accompanying software framework is engineered to rapidly compensate for measurement errors, enabling real-time assessment and calibration of the ultrasonic range unit's accuracy. Ultrasonic spectrum technology is extensively applied across diverse sectors—including engineering, agriculture, transportation, environmental monitoring, safety systems, and energy conservation—highlighting its vital role in advancing research and technological innovation. Critical performance metrics such as measurement accuracy, distance determination, and system reliability are essential for improving the maneuverability and durability of applications, while also supporting scalability and fostering scientific progress.

Currently, automotive ultrasonic barrier protection systems predominantly depend on 8-bit or 16-bit microcontroller architectures, which serve as the control units responsible for echo detection and signal processing to facilitate obstacle navigation. This research presents a comprehensive simulation-based evaluation of the proposed ultrasonic sensor device, rigorously testing its performance against anticipated operational metrics. These systematic assessments are crucial for validating the system's reliability and effectiveness in real-world scenarios, ensuring it delivers precise, dependable data for enhanced safety and efficiency in vehicle obstacle detection and related applications.

## References

- 1. Li, S. A., & Li, C. (2019). FPGA implementation of adaptive Kalman filter for industrial ultrasonic applications. Microsystem Technologies, 1-8.

- 2. Beasley, W., Gatusch, B., Connolly-Taylor, D., Teng, C., Marzo, A., & Nunez-Yanez, J. (2019). High-Performance Ultrasonic Levitation with FPGA-based Phased Arrays. arXiv preprint arXiv:1901.07317.

- 3. Herman, K., Boemo, E., Fernandez, W., Duran-Faundez, C., & Rubio, E. (2018, October). Preliminary Studies on FPGA Implementation of a Real-Time Ultrasonic Air-Coupled Sonar. In 2018 IEEE International Conference on Automation/XXIII Congress of the Chilean Association of Automatic Control (ICA-ACCA) (pp. 1-4). IEEE.

- 4. Seyedroudbari, H., Feng, X., Crongeyer, G., & Janamian, S. (2018). Design and Implementation of a Two-Dimensional Ultrasonic Radar using FPGA.

- 5. Li, W., & Zhang, H. (2017, December). A FPGA based ultrasonic rail flaw detection system. In 2017 IEEE International Symposium on Signal Processing and Information Technology (ISSPIT) (pp. 150-155). IEEE.

- 6. Hernández, Á., García, E., Gualda, D., Villadangos, J. M., Nombela, F., & Ureña, J. (2017). FPGA-based architecture for managing ultrasonic beacons in a local positioning system. IEEE Transactions on Instrumentation and Measurement, 66(8), 1954-1964. 41

- 7. Chiu, Z. K., & Lee, P. J. (2017, July). A Fuzzy control for obstacle avoidance implemented in the wheel robot with FPGA. In 2017 International Conference on System Science and Engineering (ICSSE) (pp. 95-98). IEEE.

- 8. Rao, I. N., Venkateswarlu, V., & Anuragh, V. (2017). Measurement of Distance of an Obstacle Using Ultrasonic Sensor with FPGA. International Journal of Current Research in Embedded System & VLSI Technology [ISSN: 2581-5105 (online)], 2(2).

- 9. García, G. J., Jara, C. A., Pomares, J., Alabdo, A., Poggi, L. M., & Torres, F. (2014). A survey on FPGA-based sensor systems: towards intelligent and reconfigurable low-power sensors for computer vision, control and signal processing. Sensors, 14(4), 6247-6278.

- 10. Chinnaiah, M. C., DivyaVani, G., SatyaSavithri, T., & Rajeshkumar, P. (2014, January). Implementation of Shortest path planning algorithm without track using FPGA robot: A new approach. In 2014 International Conference on Advances in Electrical Engineering (ICAEE) (pp. 1-4). IEEE.